一個系統電路要能穩定且可靠的運作,最重中之重首要關注的就是 PDN (Power distribution network) 電源分佈網路。尤其高速系統板上頭往往有數顆高度集成的晶片,且一個電源域需供電給許多功能區塊在同時運作跟傳輸,此時對於整體的 PI (Power integrity) 電源完整性規劃設計將是個不小的挑戰。

工程師們在進行電源分佈網路 PDN 設計佈局時,皆會優先參考原廠的 reference design 文件,因為零件選用與佈局原廠都經過驗證測試過了,故理論上不會出現太大的問題。但很多時候參考設計應用在自家的產品上,會因為產品功能的增減、機構外型、電路成本的考量...等等,往往電路佈局都會與參考設計有些許差異。

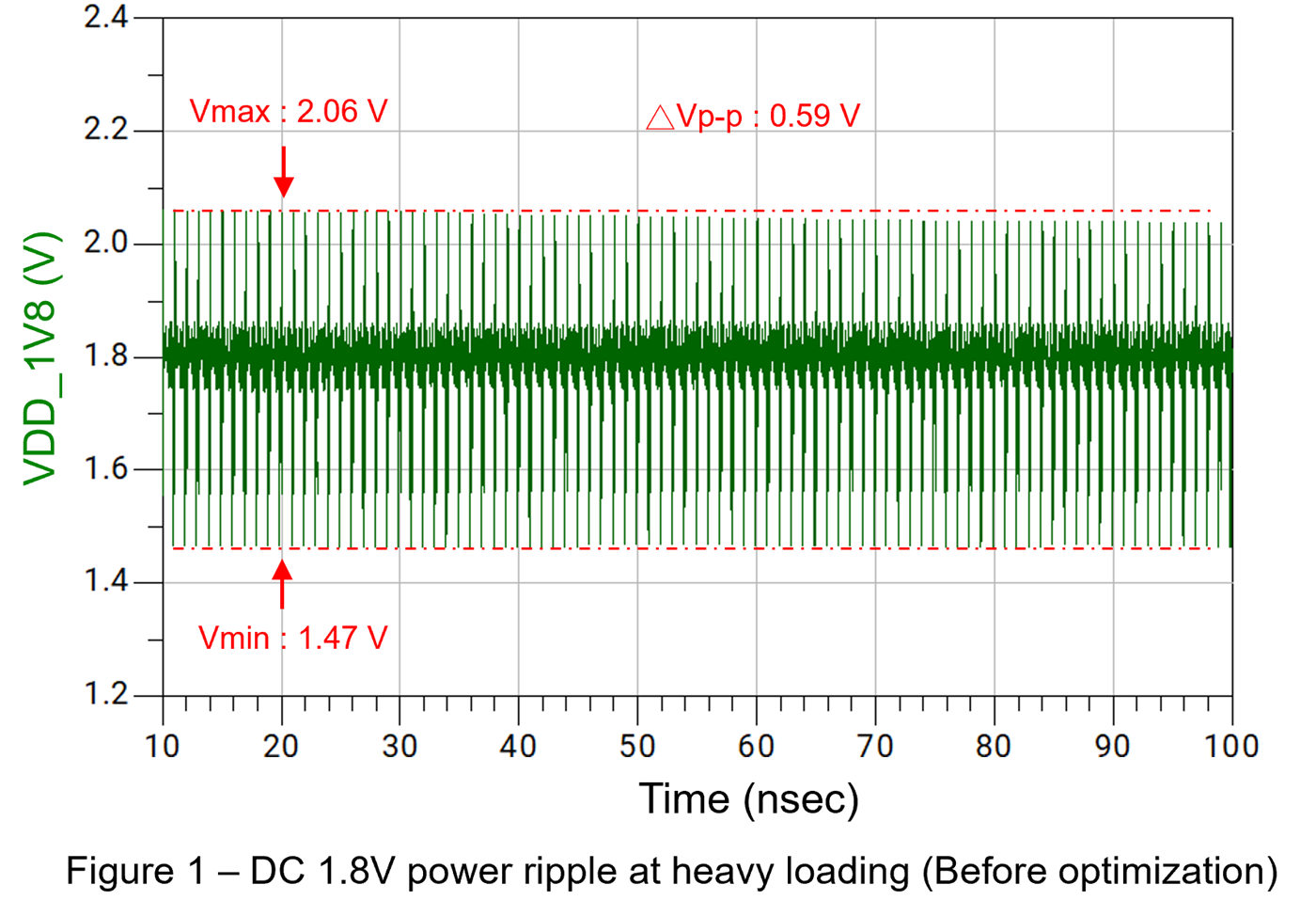

我們從圖一所示的1.8V時域波形圖可以看到,在高負載的工作模式下電源的漣波和雜訊 (Ripple & Noise) 相當嚴重,其電源最大值來到了2.06V、最小值下探到了1.47V、峰峰值則有0.59V的震盪,這樣的1.8V直流電源穩定程度確實非常不理想,也無法勝任高工作負載狀態時的電源需求。

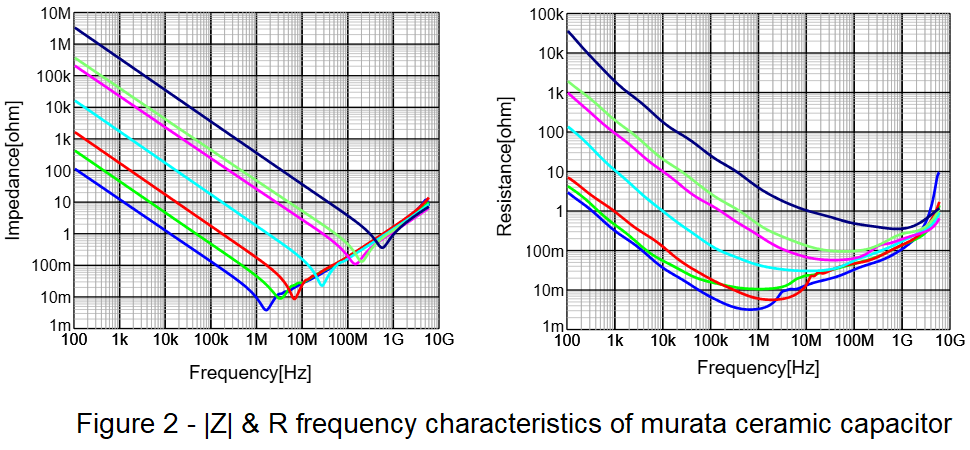

客戶端工程師反應電源的部分,皆嚴格參照原廠的設計建議及選料,電源樹 (Power tree) 功耗和耐流都有抓了Buffer,使用替代料的電容也會詳細的去對照,相關旁路/去耦電容 (Bypass / Decoupling capacitor) 的頻域特性如圖二所示,怎麼還是會有問題 ?!

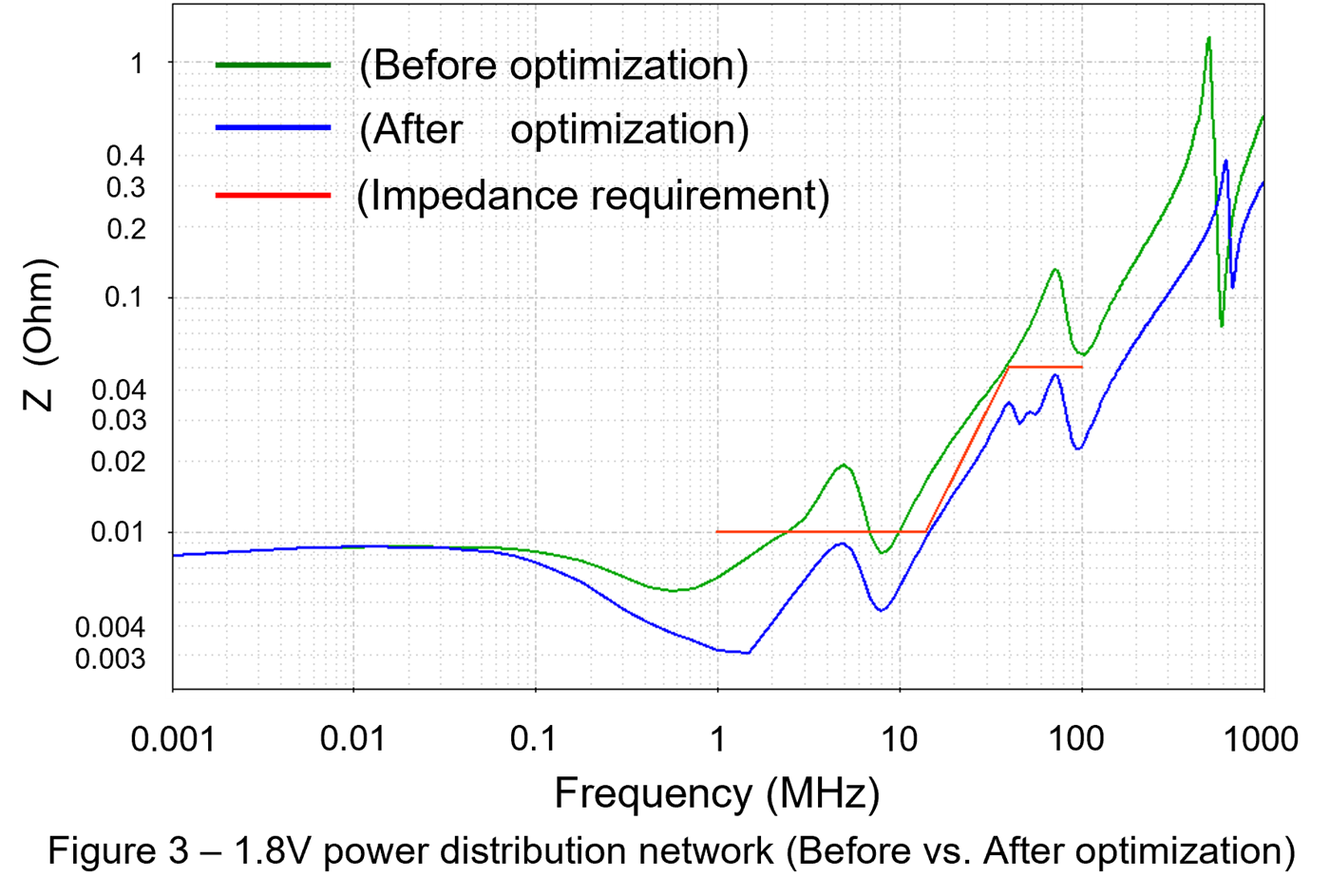

針對有問題的1.8V直流電源網路 (Power distribution network) PDN 進行分析,從圖三綠色的交流阻抗ACR曲線 (優化前) 可以看到,幾乎完全超出設計指南要求的紅色阻抗曲線 1MHz to 100MHz 頻率範圍內的規範,導致整個系統在高負載狀態下運作時,此處電源域將可能無法滿足晶片穩定工作所需的條件,並且一定程度使系統產生許多誤動作乃至造成周邊電子元器件損壞。

經過電容擺放位置與電源平面和迴流路徑的調整,優化整個電源系統的RLC寄生參數,結果如圖三藍色的交流阻抗ACR曲線 (優化後) 所示,頻段 1MHz to 100MHz 的阻抗要求已達到規範建議,且全頻段的阻抗皆有明顯的改善。在不增減電容數量的優化調整下,很多效果不彰的阻抗頻段都起了作用,由此可知電容配置的合理性與電源迴路上的寄生參數,對於 PI (Power integrity) 電源完整性優化將是個很關鍵的因素。

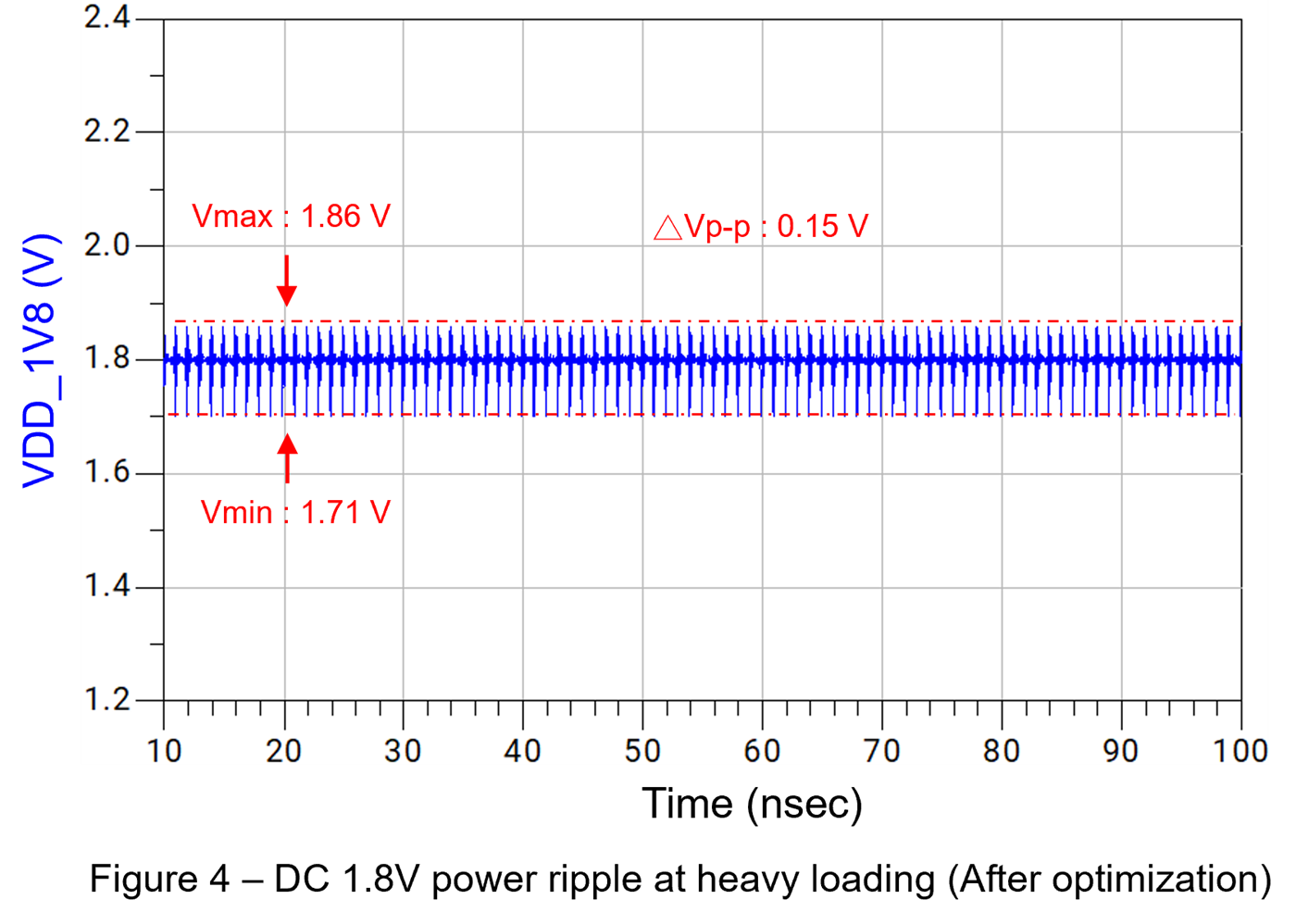

優化完後我們再觀察一下1.8V直流電源的時域波形圖,在高負載 worst-case 的模式下電源的漣波和雜訊 (Ripple & Noise) 的情況。如圖四所示可以觀察到,此電源域在重載的工作條件下,電源的穩定度有大幅度的改善,其峰峰值從0.59V下降到0.15V (震盪擺幅減少了0.44V),且最大值落在1.86V、最小值則在1.71V,皆符合1.8V電源正負5%誤差下的工作條件。

此處不僅僅解掉了1.8V的PDN電源分佈網路中的ACR交流阻抗、DCR直流阻抗、IRdrop電壓降等問題,同時也連帶地解決掉其它高速訊號的SI信號完整性問題。由於不恰當的電源佈局規劃,不僅會造成供電不穩和電源的雜訊增加,連帶著也會大幅度提高系統上的耦合干擾惡化造成嚴重的SI問題。

並且電路系統上各個電源分佈的網路,通常在PCB裡頭佔據著很大面積的導體,這樣的結構非常容易成為電磁輻射的發射源與接收源,進而造成EMI和EMC等相關問題,這也是為什麼電源分佈網路PDN在整個電路系統的設計與佈局顯得如此重要。