我們經常在PCB印刷電路板上的IC晶片旁,看到佈滿著許多不同封裝大小的MLCC多層陶瓷電容,其背後的主要目的是為了晶片運作時,將系統所需電源加以穩壓和濾波定。然而這些不同電容與規格選用,在不同的工作條件與應用場景皆有所不同,考量因素有額定電壓(Rated voltage)、工作溫度(Operating temperature)、電容值(Capacitance)、封裝(Size),還有關鍵的參數指標ESR(Equivalent series resistance)和ESL(Equivalent series inductance)。

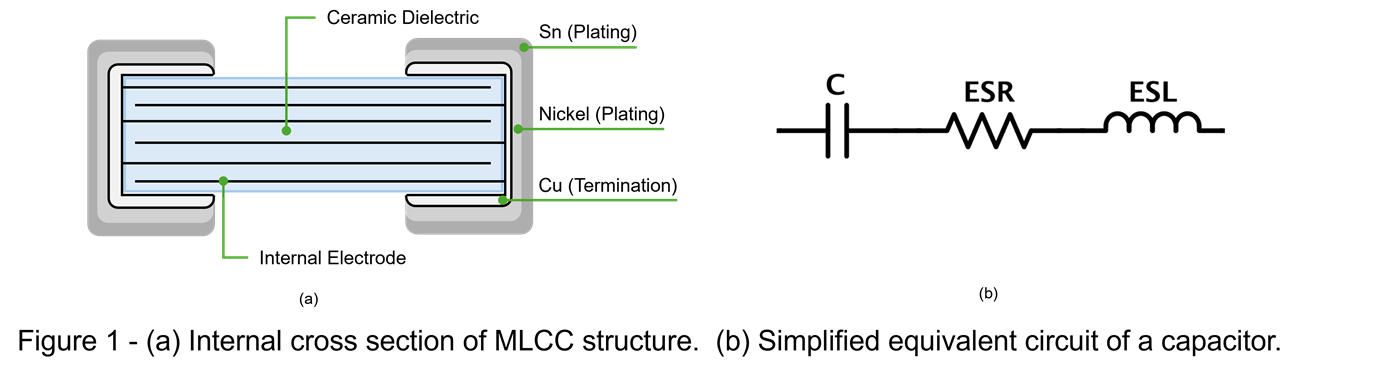

由於現實中的電容並非是理想的電容器,我們可以從圖一(a)的MLCC剖面圖可以看到,其物理結構由外到內分別為錫(Sn)、鎳(Nickel)、銅(Cu)、陶瓷介質(Ceramic dielectric)、內外電極(Electrode)等材料,層層交疊封裝的組成結構,必然也同時產生了電阻和電感的特性。故現實中的電容器,可等效成如圖一(b)的簡化電路,電容C、等效串聯電組ESR、等效串聯電感ESL三個元件串聯起來。

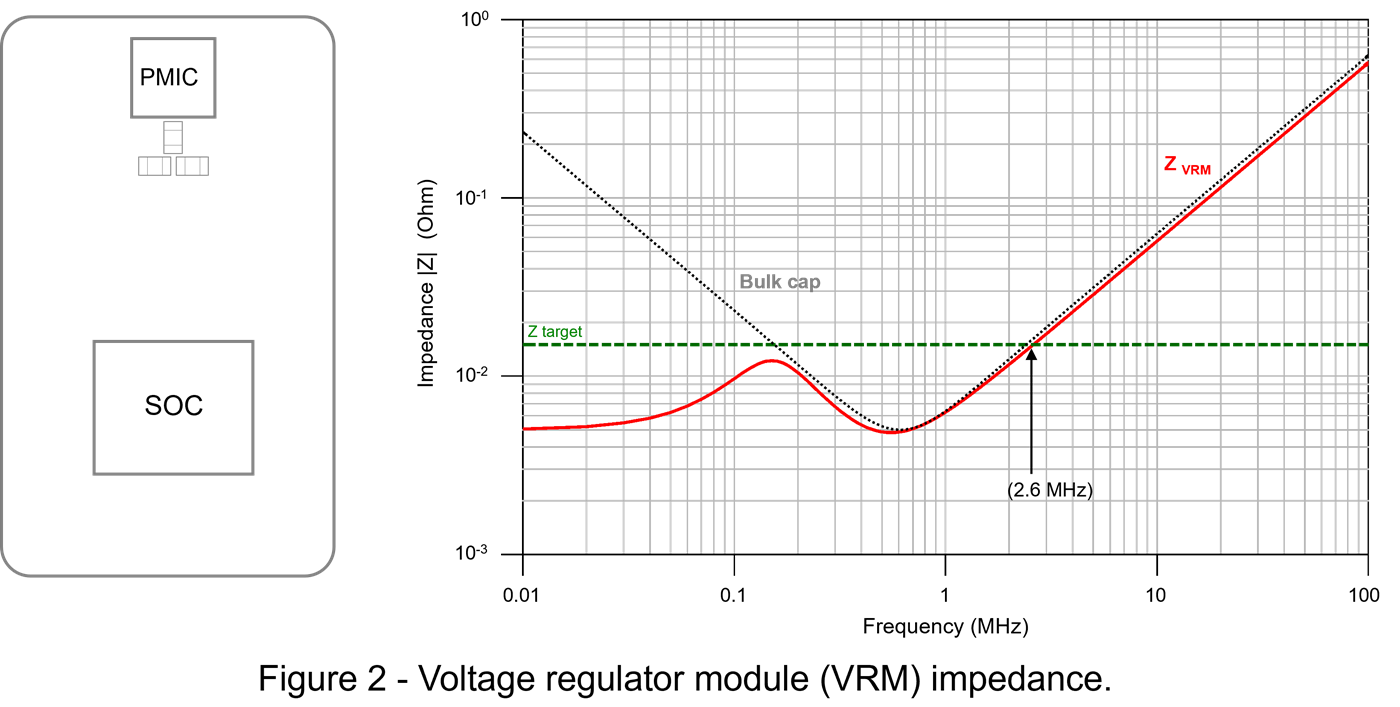

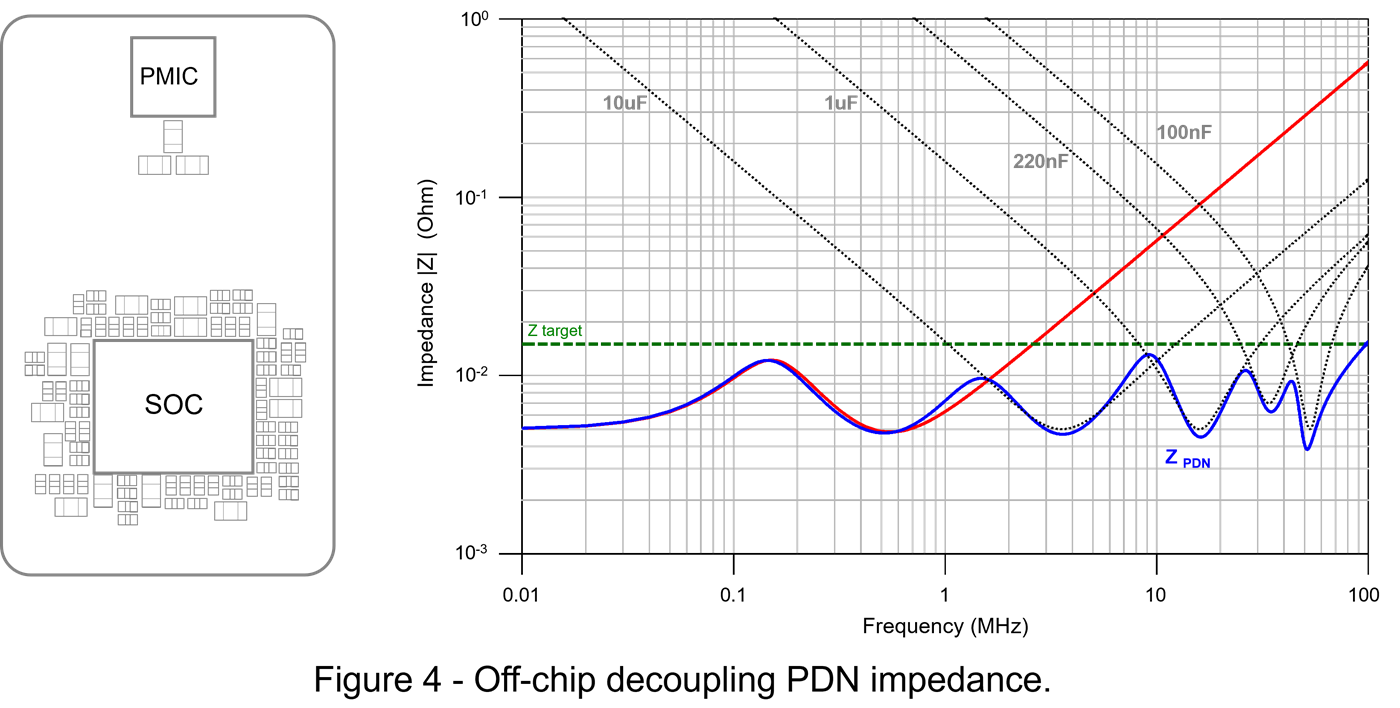

圖二所示為未加上去耦電容的SOC到供電電源VRM路徑上的示意圖和阻抗曲線,從紅色的阻抗曲線可觀察到,在頻率2.6MHz以下的阻抗皆符合目標阻抗Ztarget的要求,超過了2.6MHz以上就全部超標了。整個PDN電源供電網路,單單依靠著Bulk電容來維持穩壓的工作還是不足的。

由於高速電路的數位訊號(Digital signal)從頻域的角度來觀察,為不同頻率的弦波分量所組成,當此種寬頻訊號在傳輸時,無論是傳輸端或接收端,都將從所屬的供電電源抽取所需電流,這過程中整個供電路徑上亦有了瞬態寬頻傳輸特性的要求了。常規的改善方案就是增加電容,利用電容的阻抗特性來壓低阻抗並擴展頻寬,確保電源軌道在所需頻寬內有低阻抗的條件。

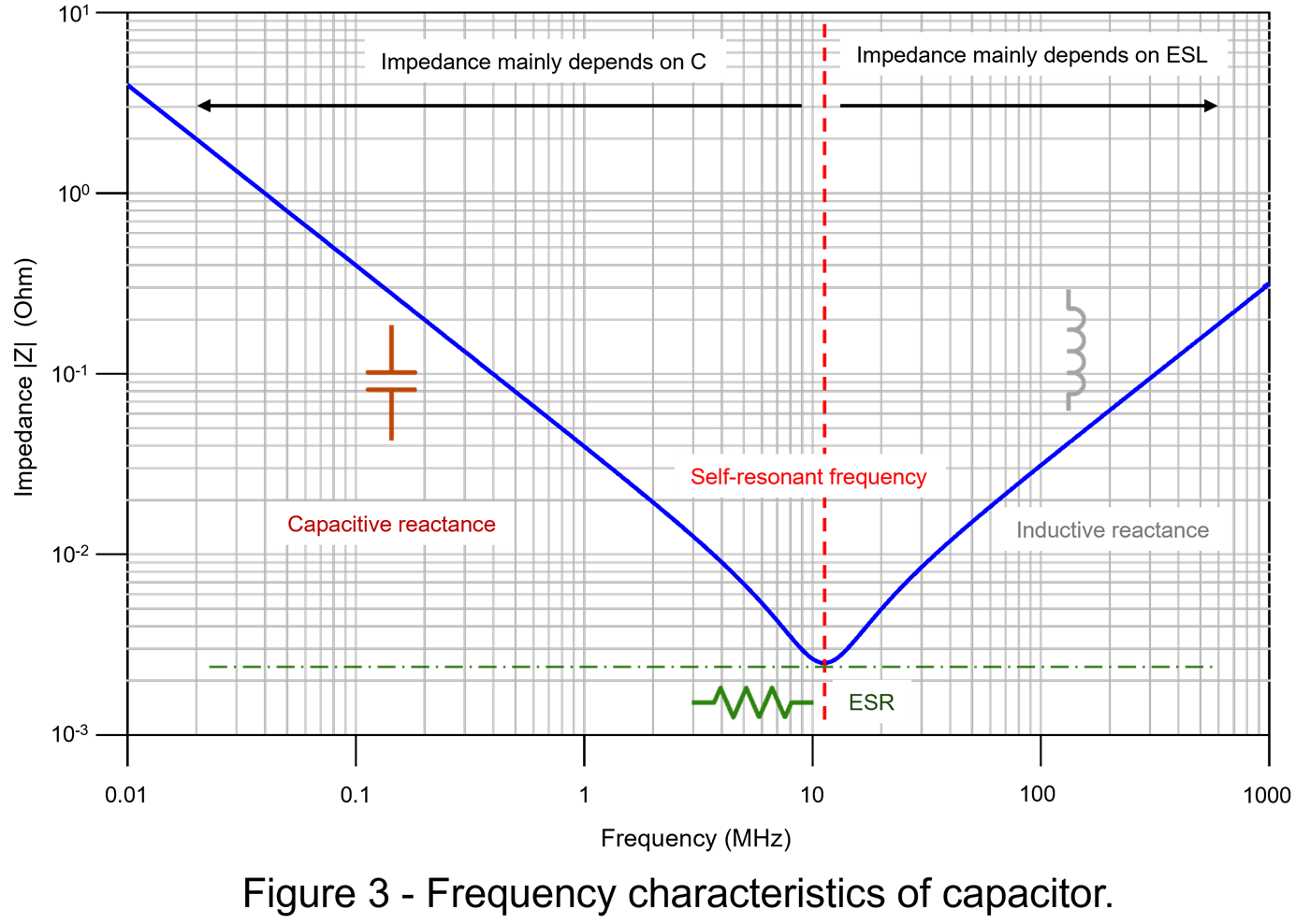

先前我們知道現實中的電容器特性,是由電容、電阻、電感等效串聯起來的綜合表現,從圖三的電容器實測阻抗曲線可以觀察到,現實中的電容器特性可分為三個部分。低頻時候的阻抗特性呈現出電容C在主導的趨勢,隨著頻率升高則阻抗降低。高頻時候的趨勢恰恰相反,而是呈現出電感ESL主導的規律特性,隨著頻率的提升其阻抗也隨之升高。

當容抗(Capacitive reactance)和感抗(Inductive reactance)之間拉鋸達到平衡相互抵消時阻抗最低,此時電容器的阻抗為ESR純電阻特性,此頻率點稱為自諧振頻點。故電容器的規格在選用評估時ESR和ESL則是個非常重要的參數,它們將決定了低阻抗(Low impedance)的能力與範圍。

正是利用電容器這樣的特性,在SOC晶片週圍加上了不同容值的電容如圖四(左)所示,來降低電源軌道的PDN阻抗曲線,達到穩壓、濾波、擴展低阻抗頻寬的目的,其結果如圖四(右)藍色曲線所示。很顯著的可以觀察到,透過10uF、1uF、220nF、100nF不同電容值的頻域阻抗特性,使得低於目標阻抗Ztarget數值的頻寬從2.6MHz擴展到了100MHz,大幅度優化了低阻抗頻寬範圍。

這樣的電源分佈網路PDN阻抗曲線,對於高數據率訊號傳輸時的瞬態負載電源需求,提供了直流電源更加穩定的供電環境與條件。至於需要選用到多小的電容值規格,多低的阻抗和頻寬範圍如 : 20MHz、50MHz、100MHz,則需要依據各家晶片廠商的要求,進一步來考量與設計了。