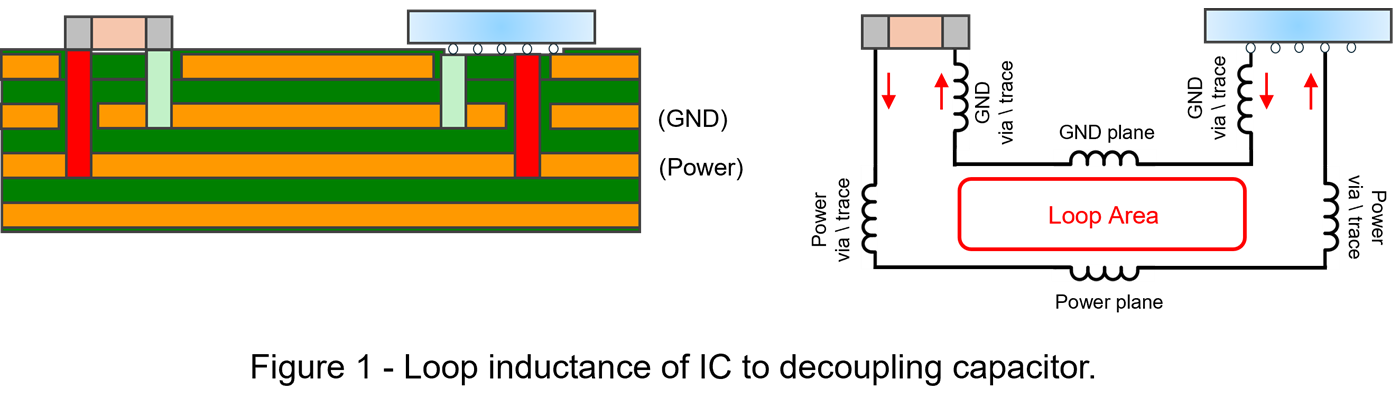

當電容安裝到PCB印刷電路板上(如圖一所示),是透過電源(Power)和地(GND)的過孔Via,連接到內層的電源平面和地平面與主晶片相互連接形成一個環路,來達到去耦與補償的作用。這整個路徑上的Trace走線、Via過孔、電源和地平面(Plane)皆存在著金屬導體本身的寄生參數特性 "電感"(Inductance),最終形成環路電感(Loop inductance)。當這些金屬導體的寄生電感值逐步增大時,將一定程度影響到電容器本身特性的整體表現,導致在進行電源網路PDN(Power distribution network)阻抗優化設計無法達到預期。

影響環路電感(Loop inductance)不外乎有幾點要特別注意,如電容器擺放位置離主晶片過遠、電容和主晶片電源走線扇出過長、電源和地平面的Via過孔配置不佳,皆會增加整體的環路電感 (Loop inductance)需盡量避免。

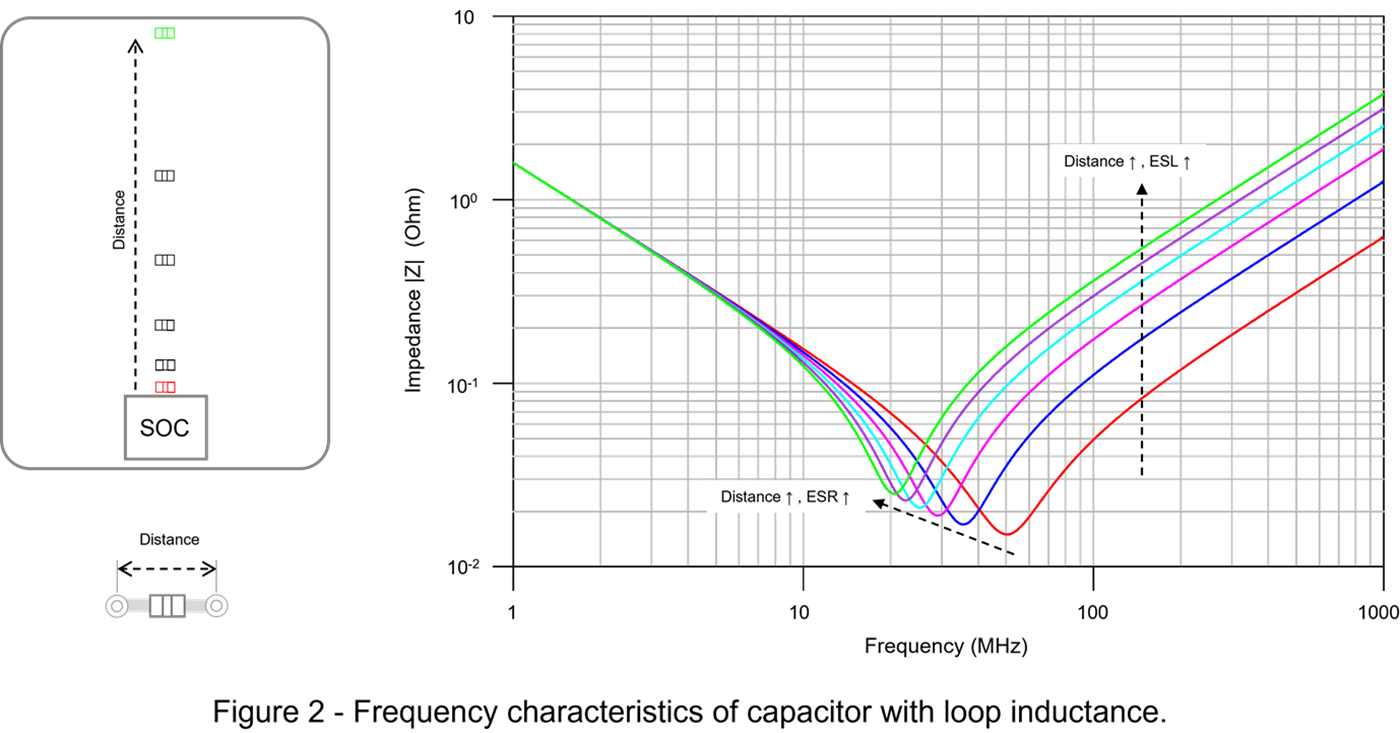

我們從圖二的電容阻抗曲線能觀察到,當電容器補償路徑上的環路電感(Loop inductance)增加,電容整體的等效串聯電感ESL增加,由感抗(Inductive reactance)主導的高頻段阻抗值也會提高。隨著電感量逐步增加,電容器的阻抗諧振頻點發生位移往低頻方向移動,並且同時也造成等效串聯電阻ESR的增大。這樣的阻抗特性改變,就是造成電源網路PDN阻抗優化困難的根本原因。

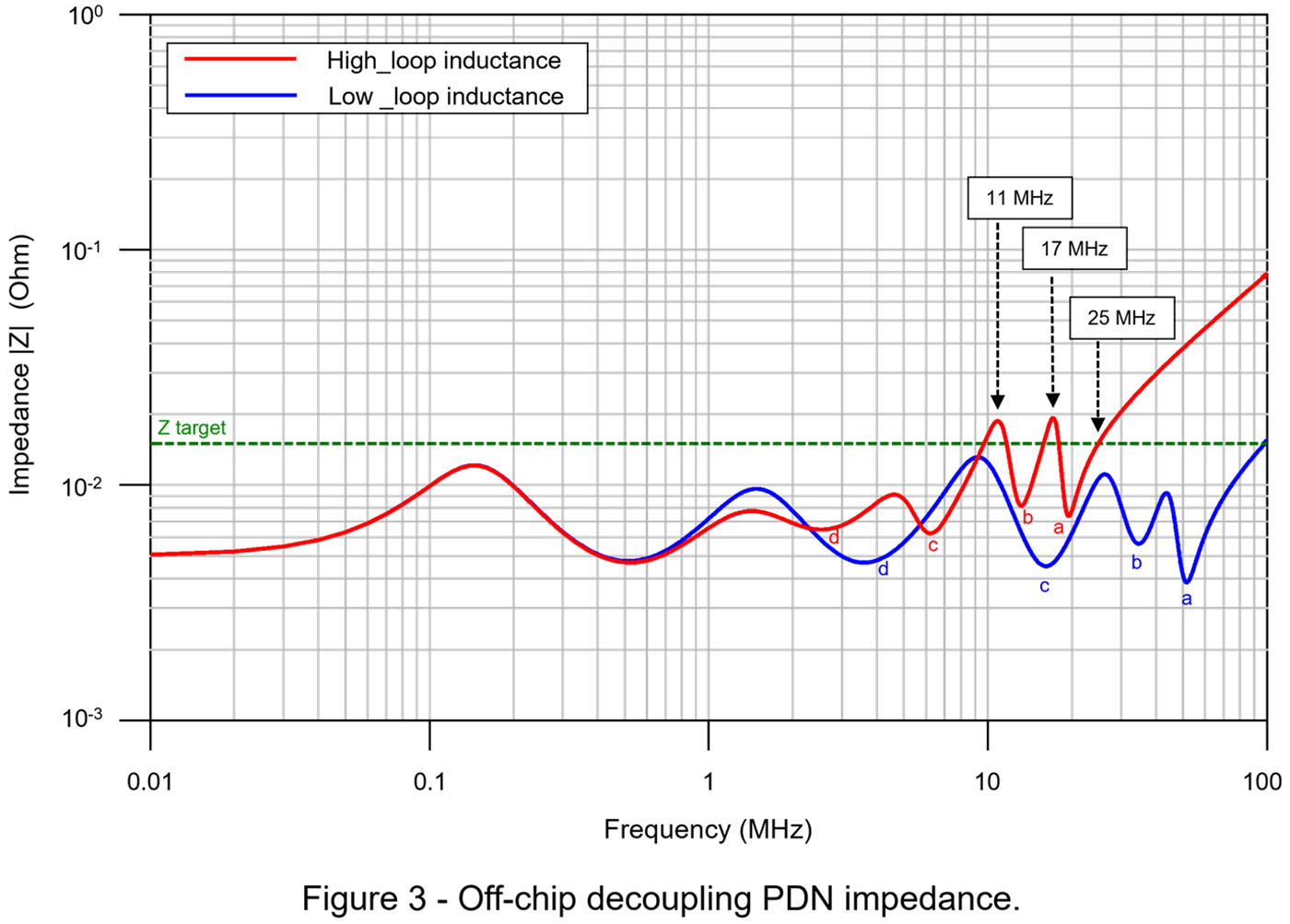

從圖三的PDN阻抗曲線可以發現,低環路電感藍色曲線在100MHz以下的阻抗表現,皆都低於Ztarget目標阻抗的要求,但在不良的高環路電感條件下如紅色曲線,在相同的電容規格配置與電容數量下卻有如此大的差異。

每個電容器所負責的頻寬與諧振頻點如圖三 a、b、c、d 位置所示,在環路電感增加的作用下都往低頻位移,以及各諧振點最低阻抗值變高。整個PDN低阻抗範圍的最高頻率範圍從100MHz降到了25MHz,整整縮減了75MHz頻寬。更糟糕的是在11MHz和17MHz位置還出現了超標的LC並聯諧振峰。

由此可以更直觀且清楚的了解到,電容器的擺放與PCB的走線Trace、過孔Via、電地平面plane所產生的寄生電感,對PDN阻抗影響甚鉅。稍沒注意很可能就導致目標阻抗無法達到要求,造成供電不穩、雜訊過大等各式各樣問題。故環路電感的控制在電源完整性設計中,是個非常重要的課題且關鍵的因素。